इलेक्ट्रॉनिक्स उद्योग ट्रांजिस्टर की संख्या की एक सीमा के करीब पहुंच रहा है जिसे कंप्यूटर चिप की सतह पर पैक किया जा सकता है। इसलिए, चिप निर्माता बाहर के बजाय निर्माण करना चाह रहे हैं।

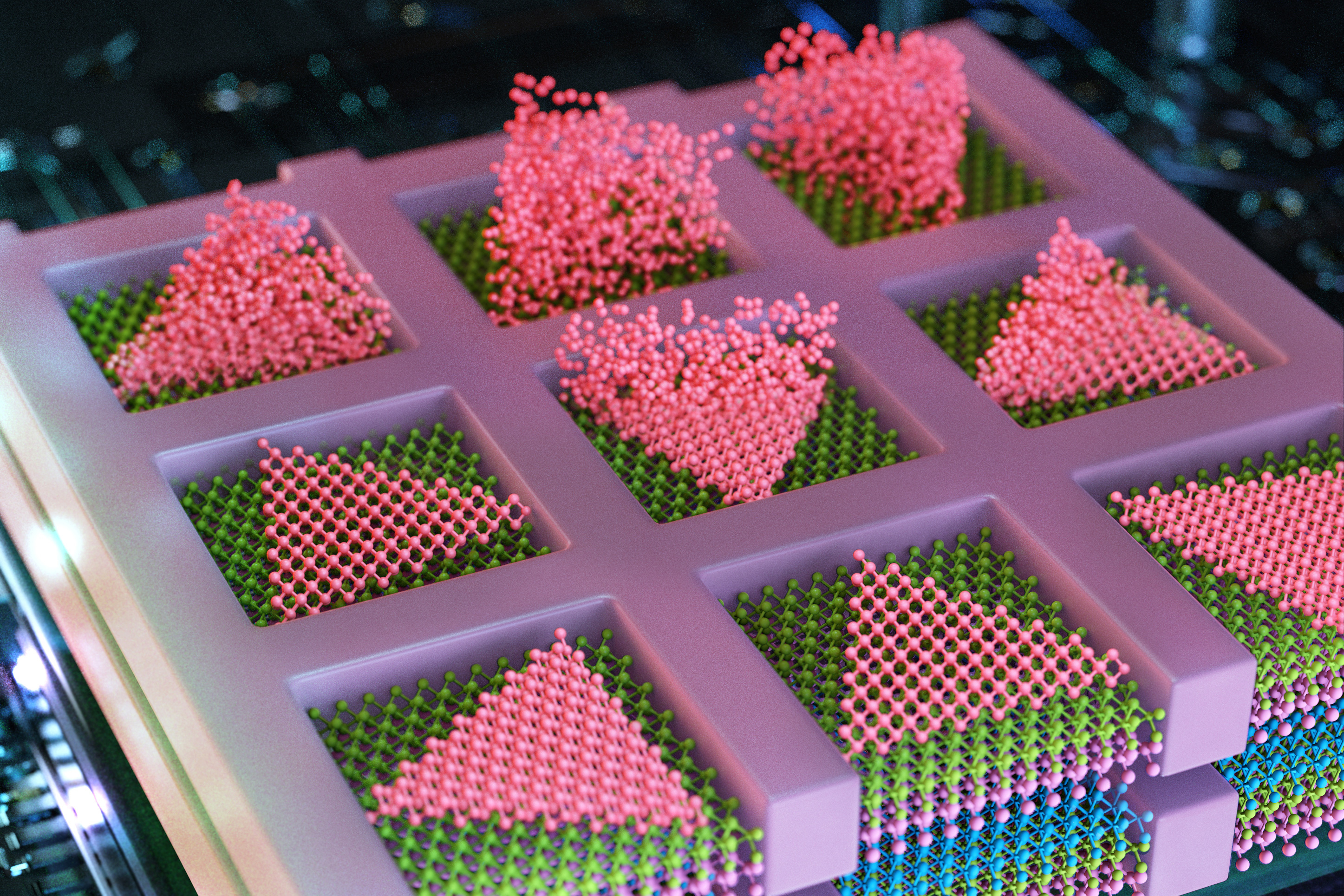

एक ही सतह पर कभी-कभी छोटे ट्रांजिस्टर को निचोड़ने के बजाय, उद्योग ट्रांजिस्टर और अर्धचालक तत्वों की कई सतहों को ढेर करने का लक्ष्य बना रहा है-एक रेंच हाउस को एक उच्च-वृद्धि में बदलने के लिए। इस तरह के बहुस्तरीय चिप्स तेजी से अधिक डेटा को संभाल सकते हैं और आज के इलेक्ट्रॉनिक्स की तुलना में कई अधिक जटिल कार्यों को पूरा कर सकते हैं।

एक महत्वपूर्ण बाधा, हालांकि, वह मंच है जिस पर चिप्स बनाया जाता है। आज, भारी सिलिकॉन वेफर्स मुख्य पाड़ के रूप में काम करते हैं, जिस पर उच्च गुणवत्ता वाले, एकल-क्रिस्टलीय अर्धचालक तत्व उगाए जाते हैं। किसी भी स्टैकेबल चिप को प्रत्येक परत के हिस्से के रूप में मोटी सिलिकॉन “फर्श” को शामिल करना होगा, कार्यात्मक अर्धचालक परतों के बीच किसी भी संचार को धीमा करना होगा।

अब, MIT इंजीनियरों ने इस बाधा के चारों ओर एक रास्ता ढूंढ लिया है, एक बहुस्तरीय चिप डिज़ाइन के साथ, जिसमें किसी भी सिलिकॉन वेफर सब्सट्रेट की आवश्यकता नहीं होती है और अंतर्निहित परत की सर्किटरी को संरक्षित करने के लिए तापमान पर पर्याप्त तापमान पर काम करता है।

जर्नल में आज दिखाई देने वाले एक अध्ययन में प्रकृतिटीम ने एक दूसरे के शीर्ष पर सीधे उगाई गई उच्च गुणवत्ता वाले अर्धचालक सामग्री की वैकल्पिक परतों के साथ एक बहुस्तरीय चिप को गढ़ने के लिए नई विधि का उपयोग करके रिपोर्ट की है।

विधि इंजीनियरों को किसी भी यादृच्छिक क्रिस्टलीय सतह पर उच्च-प्रदर्शन ट्रांजिस्टर और मेमोरी और लॉजिक तत्वों का निर्माण करने में सक्षम बनाती है-न केवल सिलिकॉन वेफर्स के भारी क्रिस्टल मचान पर। इन मोटी सिलिकॉन सब्सट्रेट के बिना, कई अर्धचालक परतें अधिक प्रत्यक्ष संपर्क में हो सकती हैं, जिससे परतों के बीच बेहतर और तेजी से संचार और गणना हो सकती है, शोधकर्ताओं का कहना है।

शोधकर्ताओं ने कल्पना की कि विधि का उपयोग एआई हार्डवेयर के निर्माण के लिए किया जा सकता है, लैपटॉप या पहनने योग्य उपकरणों के लिए स्टैक्ड चिप्स के रूप में, जो आज के सुपर कंप्यूटर के रूप में तेज और शक्तिशाली होगा और भौतिक डेटा केंद्रों के साथ बड़ी मात्रा में डेटा को स्टोर कर सकता है।

एमआईटी में मैकेनिकल इंजीनियरिंग के एसोसिएट प्रोफेसर के अध्ययन के लेखक जीहवान किम कहते हैं, “यह सफलता सेमीकंडक्टर उद्योग के लिए भारी क्षमता को खोलती है, जिससे चिप्स को पारंपरिक सीमाओं के बिना स्टैक किया जा सकता है।” “यह एआई, लॉजिक और मेमोरी में अनुप्रयोगों के लिए कंप्यूटिंग पावर में ऑर्डर-ऑफ-मैग्निट्यूड सुधार का कारण बन सकता है।”

अध्ययन के एमआईटी के सह-लेखकों में पहले लेखक की सेक किम, सेनघवान सेओ, डोयून ली, जंग-एल रियू, जेकुंग किम, जून मिन सुह, जून-चुल शिन, मिन-क्यूयू गीत, जिन फेंग, और सांघो ली शामिल हैं, जो सैमसंग एडवांस्ड इंस्टीट्यूट ऑफ टोलॉजी के कोलाबोरर्स के साथ हैं।

बीज

2023 में, किम के समूह ने बताया कि उन्होंने तैयार चिप्स पर अर्धचालक सर्किटरी की विविध स्थलाकृति के समान, अनाकार सतहों पर उच्च गुणवत्ता वाले अर्धचालक सामग्री को विकसित करने के लिए एक विधि विकसित की। जिस सामग्री को वे बढ़ाते थे, वह एक प्रकार का 2 डी सामग्री थी जिसे संक्रमण-धातु डाइचेलकोजेनाइड्स, या टीएमडी के रूप में जाना जाता था, जो छोटे, उच्च-प्रदर्शन ट्रांजिस्टर बनाने के लिए सिलिकॉन के लिए एक आशाजनक उत्तराधिकारी माना जाता था। इस तरह की 2 डी सामग्री अपने अर्धचालक गुणों को एक एकल परमाणु के रूप में छोटे के रूप में भी तराजू पर बनाए रख सकती है, जबकि सिलिकॉन का प्रदर्शन तेजी से कम हो जाता है।

अपने पिछले काम में, टीम ने सिलिकॉन वेफर्स पर अनाकार कोटिंग्स के साथ -साथ मौजूदा टीएमडी पर टीएमडी बढ़ाया। परमाणुओं को खुद को उच्च गुणवत्ता वाले एकल-क्रिस्टलीय रूप में व्यवस्थित करने के लिए प्रोत्साहित करने के लिए, यादृच्छिक, पॉलीक्रिस्टलाइन विकार के बजाय, किम और उनके सहयोगियों ने पहले एक बहुत पतली फिल्म में एक सिलिकॉन वेफर को कवर किया, या सिलिकॉन डाइऑक्साइड के “मुखौटा”, जो उन्होंने छोटे उद्घाटन, या पॉकेट के साथ पैटर्न किया। फिर उन्होंने मुखौटा के ऊपर परमाणुओं की एक गैस बह की और पाया कि परमाणु “बीज” के रूप में जेब में बस गए। जेब ने बीजों को नियमित, एकल-क्रिस्टलीय पैटर्न में विकसित करने के लिए सीमित कर दिया।

लेकिन उस समय, विधि केवल लगभग 900 डिग्री सेल्सियस पर काम करती थी।

“आपको इस एकल-क्रिस्टलीय सामग्री को 400 सेल्सियस से नीचे उगाना होगा, अन्यथा अंतर्निहित सर्किटरी पूरी तरह से पकाया और बर्बाद हो गया है,” किम कहते हैं। “तो, हमारा होमवर्क था, हमें 400 सेल्सियस से कम तापमान पर एक समान तकनीक करनी थी। अगर हम ऐसा कर सकते हैं, तो प्रभाव पर्याप्त होगा।”

निर्माणाधीन

अपने नए काम में, किम और उनके सहयोगियों ने किसी भी अंतर्निहित सर्किटरी को संरक्षित करने के लिए पर्याप्त तापमान पर एकल-क्रिस्टलीय 2 डी सामग्री को विकसित करने के लिए अपनी विधि को ठीक करने के लिए देखा। उन्हें धातुकर्म में एक आश्चर्यजनक रूप से सरल समाधान मिला – धातु उत्पादन का विज्ञान और शिल्प। जब मेटालर्जिस्ट पिघले हुए धातु को एक मोल्ड में डालते हैं, तो तरल धीरे -धीरे “न्यूक्लियेट्स”, या अनाज बनाता है जो बढ़ता है और एक नियमित रूप से पैटर्न वाले क्रिस्टल में विलय हो जाता है जो ठोस रूप में कठोर होता है। मेटालर्जिस्टों ने पाया है कि यह न्यूक्लिएशन सबसे अधिक आसानी से एक सांचे के किनारों पर होता है जिसमें तरल धातु डाली जाती है।

“यह ज्ञात है कि किनारों पर nucleating के लिए कम ऊर्जा की आवश्यकता होती है – और गर्मी,” किम कहते हैं। “इसलिए हमने भविष्य के एआई हार्डवेयर के लिए उपयोग करने के लिए धातुकर्म से इस अवधारणा को उधार लिया।”

टीम ने एक सिलिकॉन वेफर पर एकल-क्रिस्टलीय TMDs उगाने के लिए देखा जो पहले से ही ट्रांजिस्टर सर्किटरी के साथ गढ़ा गया है। उन्होंने पहले सर्किटरी को सिलिकॉन डाइऑक्साइड के एक मुखौटे के साथ कवर किया, जैसे कि उनके पिछले काम में। फिर उन्होंने मास्क की प्रत्येक जेब के किनारों पर टीएमडी के “बीज” जमा किए और पाया कि ये किनारे के बीज तापमान पर एकल-क्रिस्टलीय सामग्री में 380 डिग्री सेल्सियस के रूप में कम हो गए, जो कि केंद्र में बढ़ने लगे बीजों की तुलना में, प्रत्येक जेफ के किनारों से दूर, जो कि एकल-सिस्टरोलिन सामग्री बनाने के लिए उच्च तापमान की आवश्यकता होती है।

एक कदम आगे बढ़ते हुए, शोधकर्ताओं ने दो अलग-अलग TMDs की वैकल्पिक परतों के साथ एक बहुस्तरीय चिप बनाने के लिए नई विधि का उपयोग किया-मोलिब्डेनम डाइसल्फ़ाइड, एन-टाइप ट्रांजिस्टर बनाने के लिए एक आशाजनक सामग्री उम्मीदवार; और टंगस्टन डिसेलेनाइड, एक ऐसी सामग्री जिसमें पी-टाइप ट्रांजिस्टर में बनाए जाने की क्षमता है। P- और N- प्रकार के ट्रांजिस्टर दोनों किसी भी लॉजिक ऑपरेशन को पूरा करने के लिए इलेक्ट्रॉनिक बिल्डिंग ब्लॉक हैं। टीम दोनों सामग्रियों को एकल-क्रिस्टलीय रूप में विकसित करने में सक्षम थी, सीधे एक-दूसरे के ऊपर, किसी भी मध्यवर्ती सिलिकॉन वेफर्स की आवश्यकता के बिना। किम का कहना है कि विधि एक चिप के अर्धचालक तत्वों के घनत्व को प्रभावी ढंग से दोगुना कर देगी, और विशेष रूप से, धातु-ऑक्साइड सेमीकंडक्टर (सीएमओएस), जो एक आधुनिक लॉजिक सर्किटरी का एक बुनियादी बिल्डिंग ब्लॉक है।

“हमारी तकनीक द्वारा महसूस किया गया एक उत्पाद न केवल एक 3 डी लॉजिक चिप है, बल्कि 3 डी मेमोरी और उनके संयोजन भी है,” किम कहते हैं। “हमारे विकास-आधारित मोनोलिथिक 3 डी विधि के साथ, आप सैकड़ों लॉजिक और मेमोरी लेयर्स के लिए दसियों बढ़ सकते हैं, एक दूसरे के ऊपर, और वे बहुत अच्छी तरह से संवाद करने में सक्षम होंगे।”

“पारंपरिक 3 डी चिप्स को वफ़र के माध्यम से छेद ड्रिलिंग द्वारा सिलिकॉन वेफर्स के साथ गढ़े गए हैं-एक प्रक्रिया जो स्टैक्ड लेयर्स की संख्या, ऊर्ध्वाधर संरेखण संकल्प और पैदावार को सीमित करती है,” पहले लेखक केसोक किम कहते हैं। “हमारी वृद्धि-आधारित विधि उन सभी मुद्दों को एक साथ संबोधित करती है।”

अपने स्टैकेबल चिप डिजाइन को आगे बढ़ाने के लिए, किम ने हाल ही में एक कंपनी, FS2 (भविष्य के सेमीकंडक्टर 2 डी सामग्री) को बंद कर दिया है।

“हम अब तक एक छोटे पैमाने पर डिवाइस सरणियों में एक अवधारणा दिखाते हैं,” वे कहते हैं। “अगला कदम पेशेवर एआई चिप ऑपरेशन दिखाने के लिए स्केलिंग कर रहा है।”

इस शोध को सैमसंग एडवांस्ड इंस्टीट्यूट ऑफ टेक्नोलॉजी और यूएस एयर फोर्स ऑफिस ऑफ़ साइंटिफिक रिसर्च द्वारा भाग में समर्थन किया गया है।

।